最近公布的一項專利技術(shù)表明,英特爾正在研究一種新的晶體管設計---堆疊叉板(Forksheet)晶體管。

堆疊叉板晶體管可以實現(xiàn)垂直堆疊的3D CMOS結(jié)構(gòu),相比目前最先進的三柵極設計,雖然也很難縮小晶體管的體積,但可以增加更多的晶體管數(shù)量。

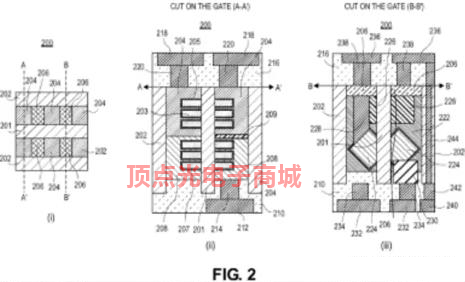

該項專利技術(shù)主要是對納米帶晶體管與鍺原子薄膜進行配對使用,鍺原子薄膜充當了介電壁。鍺原子薄膜對垂直堆疊的各層晶體管進行了物理分隔,充當p-柵極溝槽和n-柵極溝槽之間的絕緣體。通過這種設計,可以使NMOS器件和PMOS器件排列的更加緊密,且不影響各自的功能,這樣就可以節(jié)省出更多空間,也就是說,可以增加更多的晶體管數(shù)量。

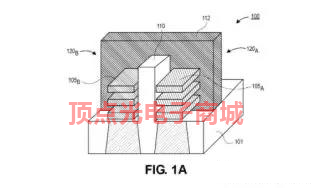

英特爾堆疊叉板(Forksheet)晶體管

早在2019年,英特爾就在一次電子設備展上展示了該技術(shù)。當時,該技術(shù)還處于探索階段,任何關(guān)于堆疊叉板技術(shù)是如何提高晶體管密度、性能和效率的具體數(shù)據(jù)都無法找到。

不過,英特爾并不是唯一一家研究該技術(shù)的公司。比利時微電子研究中心(IMEC)的一個研究小組也在同一年宣布,他們研究得到了一個專門用于堆疊叉板設備的標準單元模擬數(shù)據(jù)。IMEC的研究數(shù)據(jù)是在英特爾這項專利的基礎(chǔ)之上進行的。

堆疊叉板晶體管的平面圖和橫截面圖

比利時微電子研究中心的標準單元模擬數(shù)據(jù)表明,相比傳統(tǒng)納米片技術(shù),當采用2nm技術(shù)節(jié)點時,堆疊叉板晶體管技術(shù)可以顯著提高晶體管的密度。這表明,在2nm及以下技術(shù)節(jié)點,堆疊叉板晶體管技術(shù)可以大幅提升芯片的性能,尤其是在不同晶體管架構(gòu)需要考慮精確的蝕刻分辨率的時候。

比利時微電子研究中心(IMEC)

英特爾的研究時間是非常充裕的,對堆疊叉板晶體管技術(shù)的研究至少持續(xù)到了2020年6月。雖然我們現(xiàn)在還不知道英特爾是否會選擇堆疊叉板架構(gòu)來進行2nm工藝的研發(fā),但既然英特爾已經(jīng)公布了該項技術(shù)專利,就肯定已經(jīng)規(guī)劃好了該項技術(shù)的使用目的。

鄂公網(wǎng)安備 42011502001385號 鄂ICP備2021012849號

鄂公網(wǎng)安備 42011502001385號 鄂ICP備2021012849號