頂點光電子商城2024年11月25日消息:臺積電近期宣布N2P IP準備就緒,客戶現可設計性能增強型2nm芯片。這一消息標志著臺積電在先進制程技術方面取得了重要進展,為芯片設計廠商提供了更多選擇和可能性。

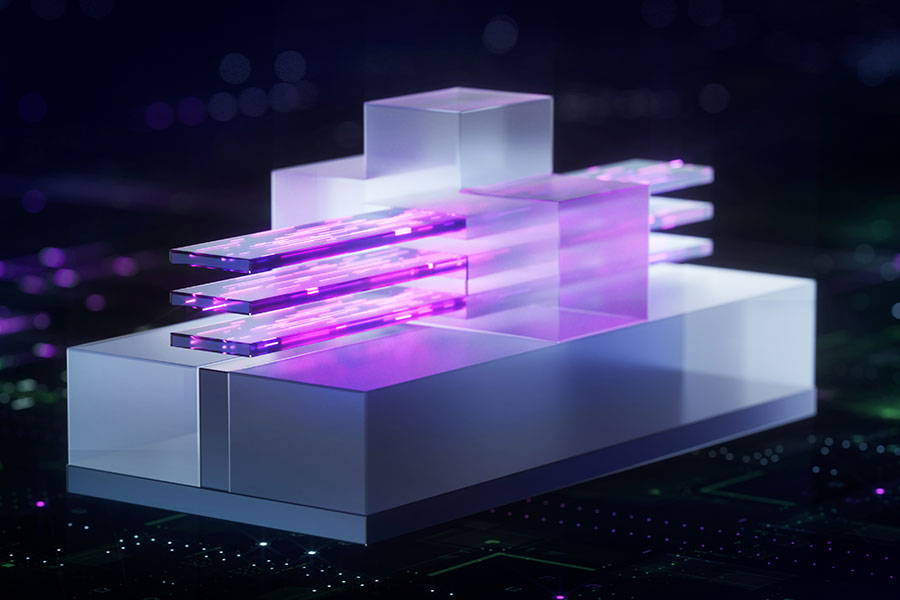

臺積電推出的N2P和N2X制程技術,是其在2納米級領域的重要布局。這兩種制程技術都采用了先進的納米片全柵極(GAA)晶體管和超高性能金屬-絕緣體-金屬(SHPMIM)電容,從而實現了性能的大幅提升。

臺積電宣布,電子設計自動化(EDA)工具和第三方IP模塊已為N2P和N2X制程技術做好準備。這意味著各種芯片設計廠商現在可以基于臺積電第二代2nm級生產節點開發芯片,充分利用GAA晶體管架構和低電阻電容器的優勢。目前,Cadence和Synopsys的所有主要工具以及Siemens EDA和Ansys的仿真和電遷移工具,都已為臺積電的N2P制造工藝做好準備。

與初代N2相比,N2P在相同功率和晶體管數量下,功耗降低5%10%或性能提高5%10%。而N2X則擁有比N2和N2P更高的FMAX電壓,為數據中心CPU、GPU和專用ASIC等設備提供了更好的性能保障。在IP級別上,N2P和N2X是兼容的。這意味著打算使用N2X的公司無需重新開發為N2P設計的任何東西,從而降低了開發成本和時間。

臺積電表示,N2P工藝預計將于2026年下半年投入大規模生產。目前,這些工藝已經通過N2P工藝開發套件(PDK)版本0.9的認證,被認為足夠成熟。此外,臺積電還積極與第三方IP供應商合作,提供包括標準單元、GPIO、SRAM編譯器、ROM編譯器、內存接口、SerDes和UCIe產品等在內的預硅設計套件,以滿足芯片設計廠商的需求。

隨著臺積電N2P和N2X制程技術的推出和EDA工具及第三方IP模塊的準備就緒,各種芯片設計廠商現在可以基于這些先進的制程技術開發出性能更強大、功耗更低的芯片產品。這將有助于推動整個半導體行業的進步和發展。

綜上所述,臺積電N2P IP準備就緒標志著其在先進制程技術方面取得了重要突破。隨著這些技術的不斷成熟和量產計劃的推進,我們有理由相信未來會有更多高性能、低功耗的芯片產品問世。

鄂公網安備 42011502001385號 鄂ICP備2021012849號

鄂公網安備 42011502001385號 鄂ICP備2021012849號