頂點資訊2021年11月5日消息,臺積電近日表示,預計于2022年實現制程工藝5nm的小外形集成電路(SOIC)研發。

臺積電一直都是采用垂直分工模式,其下游的封裝都是交由合作伙伴完成。去年,臺積電就實現了5nm制程工藝晶圓的量產。此次爆出臺積電要進行先進封裝技術的研發,是不是有點意外?

2020年8月,臺積電就透露了關于3D Fabric的消息。據悉,目前臺積電正在建造全新的3D Fabric先進封裝測試制造基地,為系統級芯片(SOC)提供先進封裝,包括5nm及以下的Chiplet整合解決方案。

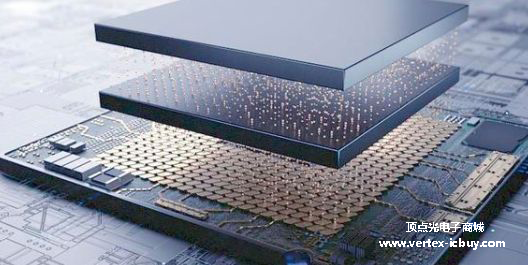

臺積電3D Fabric技術

在獨立的晶圓裸片上設計和實現不同的die(芯片裸片,具備一定功能的小型電路)就是Chiplet,我們可以稱之為小芯片。不同的晶圓裸片可以使用不同的工藝節點,甚至由不同的供應商提供。臺積電的3D Fabric技術就是將Chiplet像搭積木一樣集成封裝在一起,形成一個SOC。

目前,先進制程工藝正朝著3nm及以下邁進,采用先進封裝的小芯片正是臺積電研發3nm工藝的必要手段。

3D Fabric封裝測試制造基地將包括SOIC、2.5D先進封裝(InFO、CoWoS)和先進測試三個部分組成。為了保證在2022年順利進行SOIC,今年底,臺積電就需要完成廠房建設和設備安裝。至于2.5D先進封裝廠房,預計將在2022年完成。

目前,臺積電已經完成了3D Fabric生態系的構建,包括封裝設備、材料、記憶體和基板等。

在3nm制程工藝研發的關鍵節點,為了保證行業的領先地位以便與三星進行競爭,臺積電已經開發了3nm工藝的過渡版本---5nm強化工藝N5P。通過3D Fabric平臺,臺積電將可以為像蘋果這樣的高端客戶,提供從先進工藝節點到測試,再到先進封裝的一整套芯片解決方案。

>>>相關閱讀:IDM與垂直分工---集成電路的模式之爭 中國封測行業逐步崛起

>>>相關閱讀:國內部分封測企業已達國際領先水平 上游產業發展讓封測企業持續受益

>>>相關閱讀:2022年3nm芯片雙雙出片 三星與臺積電誰會取得優勢

鄂公網安備 42011502001385號 鄂ICP備2021012849號

鄂公網安備 42011502001385號 鄂ICP備2021012849號